Invite for Global Design Contest

The Design & Verification Conference & Exhibition is the premier conference on the application of languages, tools, methodologies and standards for the design and verification of electronic systems and integrated circuits. The focus of this highly technical conference is on the practical aspects of these technologies and their use in leading-edge projects to encourage attendees to adopt similar techniques to improve their own design and verification flows.

This invite for the design contest, titled “VEGA microprocessor (RISC-V) based Design & Verification Challenge” presents some unique opportunities for academic students:

1. Achieve deeper understanding of RISC-V architecture, indigenous VEGA Microprocessor and ecosystem.

2. Explore the design and verification space for better performance.

3. Implement your own AI hardware accelerator on industry standard FPGA in the areas such as Robotics, Healthcare, autonomous driving, sports tech, smart transportation and any other innovative application of AI

4. Opportunities to interact with experts from industry and academia.

5. To win cash prizes and potential intern opportunities at leading-edge VLSI and sponsor companies

VEGA is a series of high-performance processors including India’s first indigenous 64-bit multi- core RISC-V based Superscalar Out-of-order Processor, developed by C-DAC as part of the Digital India RISC-V (DIR-V) program by the Ministry of Electronics and Information Technology (MeitY), Govt. of India. These high-performance processors are based on the open-source RISC-V Instruction Set Architecture with Multilevel caches, Memory Management Unit and Coherent Interconnect. Six processors are currently available in the VEGA series, 32- bit Single Core 3-stage In-order, 32-bit Single Core 5-stage In-order, 64-bit Single Core 6-stage In-order, 64-bit Single Core 16-stage Out-of-Order Superscalar, 64-bit Dual Core 16-stage Out- of-Order Superscalar and 64-bit Quad Core 16-stage Out-of-Order Superscalar. These indigenous microprocessors employing the state-of-the-art architecture have a performance which is at par with other commercially available processors. The microprocessors are available as soft IPs and are amenable/ customizable for better performance/power targeted for various strategic/industrial/commercial applications.

The design contest is to be conducted virtually:

- Problem statement solution will be based on RTL Design, Functional verification, and implementation on an FPGA.

- Each team with maximum of 3 members should register and will be given four months with specific milestones for completion in multiple stages.

- The milestone details will be published along with the problem statement.

- There will be mentoring sessions at different milestones during the contest duration.

- Remote access to Genesys 2 FPGA Board and simulator/synthesizer will be provided

Congratulations to Design Contest Stage 2A winners!

| Team number | Team members | Team name | Affiliation |

|---|---|---|---|

| 0526 | Sreejita Deb, Paulami Nayek and Suprotim Datta | BINARY BRAINS | JADAVPUR UNIVERSITY, Kolkata |

| 8240 | Kuruppumullage Don Supun Dasantha Kuruppu, Dakshina Tharindu and Anuki Chamathka Pasqual | BitWeavers | University of Moratuwa, Sri Lanka |

| 4545 | Amritha Anujan, Mukesh Reddy Daram and Sangeerthana K | InnoVega I2CS | IIIT Kottayam |

| 6136 | Sakshi Thakur, Chandra Prakash and Ankit Sharma | VEGAmind | IIT Jodhpur |

| 7247 | Varshika Varshika, Gunjan Paul and Ayandeep Dutta | Silicon Savants | Kalinga Institute Of Industrial Technology, Bhubaneshwar |

| 8796 | Harshavardhan Reddy Narra, Sathwik Reddy Yadla and Surya Anirudh Gadhiraju | Team Ash | JNTUH College of Engineering, Hyderabad |

| 7548 | Sameer Srivastava, Shiven Kashyap and Satvik Tandon | Sophon | Vivekananda Institute of Professional Studies, New Delhi |

| 8623 | Sohan Pagar, Samhita Patil and Aditya Mathuriya | Sillycon | Sardar Vallabhbhai National Institute of Technology, Surat |

| 1053 | Ramith Laksara, Dinith Mayadunna and Ruwinda Nanayakkara | Mukasa | University of Peradeniya, Sri Lanka |

REGISTRATION PROCESS

This Design contest is open only for students who are currently enrolled in educational institutions pursuing BTech/BE 2nd/3rd year, 1st year MTech/MS and PhD scholars

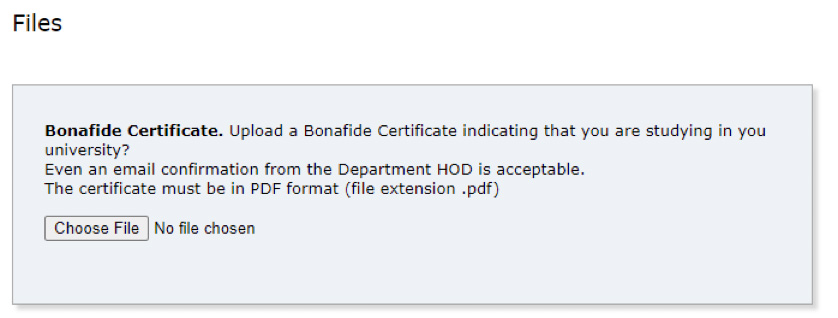

Each participant should upload a Bonafide certificate or email of their student status from the University/College by May 15, 2025

Register via the EasyChair – Register Here by February 28, 2025 March 5, 2025.

Please refer to appendix section for registration guidelines

IMPORTANT DEADLINES

February 15, 2025: Registrations for Design Contest open

March 5, 2025: Last Date for Registrations for Design Contest

March 7, 2025: Problem Statement announcement

March 10 – March 31st, 2025: Stage 1 – Planning and Idea submission

April 7, 2025: Announcement of Stage 1 result

April 7 – May 15, 2025: Stage 2 – Idea Implementation & Simulation

May 15, 2025: Final date for Stage 2 Results submission

June 10, 2025: Announcement of Stage 2 result

June 10 – July 31, 2025: Stage 3 – Hardware implementation

Sept 10, 2025: Results to be announced at Conference.

STAGES

Stage-1: Planning & Idea Submission

- Your idea submission should cover

- Detailed description of the algorithm and its design feasibility along with an overall block diagram of your idea

- Benefits and value addition of your proposed solution

Stage-2: Idea Implementation & Simulation

- Simulation of the proposed application.

Stage-3: Hardware implementation

- Synthesis of the design and implementation on FPGA

- Demonstration of the application

SELECTION CRITERIA

The winners will be selected by the judges from DVCon India with weightage on complexity of the algorithm, usefulness of the application, innovation and design feasibility.

CASH AWARDS

- INR 60,000 for the Winning team

- INR 42,000 for First Runner up

- INR 30,000 for the Second Runner up

The top three winners will be given free registration to DVCon India 2025 and opportunity to demonstrate the Design Contest solution at DVCon 2025

CONFERENCE SCHEDULE

- September 10, 2025 — Tutorials and Panels

- September 11, 2025 — Tutorials, Technical papers & Poster Session, Award Winners

Design Contest Chair

Seru Srinivas

Marvell

ssrinivas@marvell.com

Academia Collaboration Chair

Dr. Vivek Chaturvedi

IIT Palakkad

vivek@iitpkd.ac.in

Academia Collaboration Co-Chair

Prof. Sivanantham S

VIT Vellore

ssivanantham@vit.ac.in

Academia Collaboration Co-Chair

Dr. Sharad Sinha

IIT Goa

sharad@iitgoa.ac.in

C-DAC Liaison

Krishnakumar Rao S

C-DAC Thiruvananthapuram

raokk@cdac.in

SriLanka Liaison Chair

Upul Ekanayaka

ACCELR

upul.ekanayaka@accelr.site

APPENDIX

Guidelines for DVCon India 2025 – Design Contest Registration

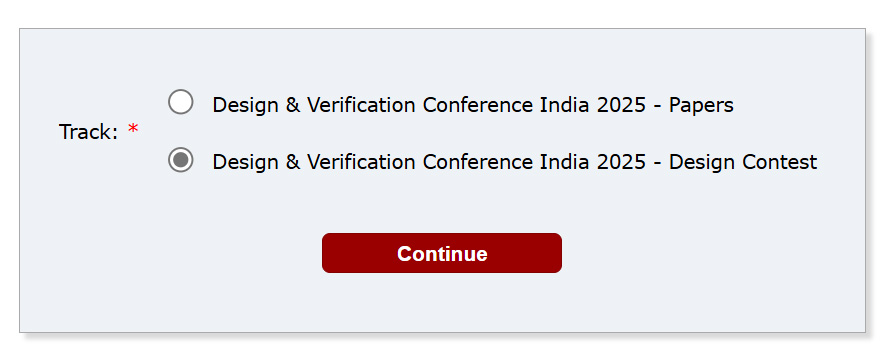

Step 1: Select the DVCon India 2025 – Design Contest Track

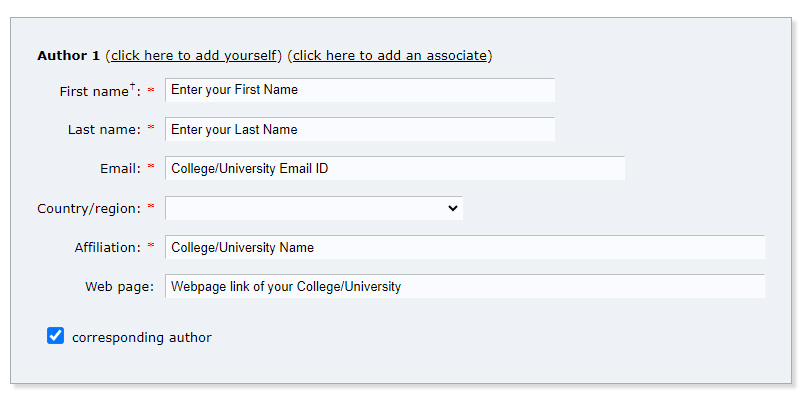

Step 2: Enter the Team Member Details (3 Team Member details needed)

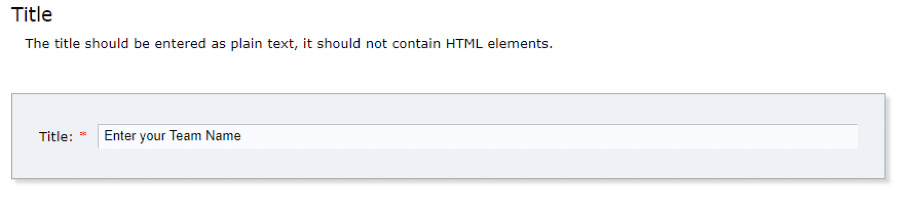

Step 3: Enter your Team name in the Title Field

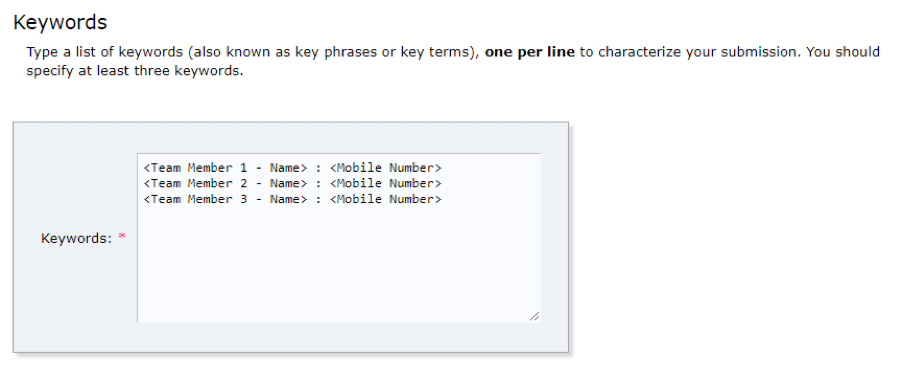

Step 4: Enter the Team Member Names and their phone numbers as indicated below.

Step 5: Upload the Bonafide Certificate from your college. (This can be done later)

COUNTDOWN

Days Until Conference

#DVCONINDIA